Werbung

Gerade erst hat AMD seine Zen-5-Familie mit den EPYC-4005-Prozessoren abgeschlossen, da kommt der für seine Leaks bekannte, aber nicht immer ganz treffsichere YouTuber Moore's Law Is Dead um die Ecke und lässt die ersten Informationshappen zur Zen-7-Architektur fallen. Dabei ist noch nicht viel über die Zen-6-Architektur bekannt, die für 2026 die Basis für AMDs Ryzen- und EPYC-Prozessoren bilden soll.

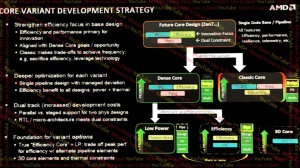

Demnach will AMD mit dem Zen-7-Design eine weitere Aufspaltung in verschiedene Kern-Klassen durchführen. Mit der Zen-4-Architektur führte AMD die dichter gepackten und sparsameren Zen-4c-Kerne ein. Diese Strategie wurde für die Zen-5-Architektur fortgesetzt und auch für Zen 6 ist davon auszugehen, dass AMD hier wieder zweigleisig fährt.

Mit der Zen-7-Architektur soll es die klassischen Zen-7-Kerne geben. Diese werden durch die Dense-Cores ergänzt, die sich wiederum in eine "Low Power"- und "Efficiency"-Variante aufteilen. Alternative "Pipeline Elemente" in der Auslegung der Kerne und Bibliotheken sollen dazu führen, dass AMD hier eine weitere Unterscheidung machen kann.

In der Fertigung sollen die CCDs mit den Zen-7-Kernen TSMCs A14-Prozess verwenden. Hier wird TSMC nach der Fertigung in A16 ebenfalls ein Backside Power Delivery Network zum Einsatz bringen. Ursprünglich war dies bereits für die N2-Fertigung geplant, wurde aber auf den A16-Prozess verschoben. Die unterhalb der CCDs eingesetzten SRAM-Chips für den 3D V-Cache wiederum sollen mit der Zen-7-Generation auf N4 von TSMC setzen. Dies kommt uns ein wenig zurückhaltend vor, denn für eine SoIC-Integration sieht TSMCs Fahrplan für eine Fertigung in A14 vor, dass hier N2-Chiplets als SRAM-Erweiterung zum Einsatz kommen.

Hinsichtlich der Ausstattung mit Cache soll Zen 7 2 MB an L2-Cache pro Kern zur Verfügung stellen – bei der Zen-5-Architektur sind es aktuell 1 MB pro Kern. Per 3D V-Cache ist eine Erweiterung des L3-Cache auf 7 MB pro Kern geplant. Je nach CCD-Variante sind es aktuell aber auch schon 12 MB L3-Cache pro Kern (32 + 64 MB für das CCD mit 3D V-Cache und Zen-5-Kerne) bzw. 2 MB pro Kern bei einem CCD mit 16 Zen-5c-Kernen und 32 MB L3-Cache insgesamt.

Eine nicht näher genanntes Modell eines EPYC-Prozessors mit Zen-7-Kernen soll über 33 Kerne je CCD verfügen und somit 264 Kerne insgesamt zu bieten haben. Demnach kämen hier acht CCDs zum Einsatz. Aktuell bietet AMD in der EPYC-9XX5-Serie mit Zen-5c-Kernen bis zu 192 Kerne insgesamt (verteilt auf 12 CCDs) und mit den klassischen Zen-5-Kernen bis zu 128 Kerne insgesamt (verteilt auf 16 CCDs). Als IOD soll der gleiche zum Einsatz kommen, wie er ab 2026 für EPYC Venice verwendet wird – zumindest spricht das Gerücht von einer Kompatibilität.

Der Tape Out der ersten Chips soll für Ende 2026 geplant sein. Es dürfte danach aber noch mehr als ein Jahr dauern, bis die ersten finalen Produkte auf den Markt kommen. Erst vor wenigen Wochen zeigten sich AMD und TSMC gemeinsam und präsentierten die ersten in N2 gefertigten CCDs mit Zen-6-Kernen für die ab 2026 erwartete Venice-Generation.

Ominöser 3D Core

Ebenfalls erwähnt und auf dem Folien zu erkennen ist ein ominöser "3D Core" und auch ein "PT Core" ist zu sehen. Was genau hier gemeint ist, wird nicht so wirklich ersichtlich. Auf den gleichen Bildern ist aber eine mögliche Umsetzung eines zusätzlichen Caches zu erkennen und hier auch die Rede von den 7 MB Slices pro Kern.

Das, was wir hier zu Gesicht bekommen, ist eine wohl noch recht frühe Planungsphase zur Zen-7-Architektur. Was sich genau daraus letztendlich auch manifestieren wird, bleibt abzuwarten. Wie immer bei Gerüchten sind diese mit Vorsicht zu genießen.